The HI-6300 is a MIL-STD-1553 / MIL-STD-1760 IP core for military and commercial applications. The core is based on Holt’s independently-validated monolithic protocol ICs for MIL-STD-1553, namely Holt’s HI-6130 and MAMBATM families, and is fully software compatible with them.

The HI-6300-xxx-C core offers an independently validated Bus Controller (BC) and Remote Terminal (RT) with a synchronous host interface. The terminal communicates with the MIL-STD-1553 buses through a shared dual bus transceiver, HI-1587, and external transformer, also available from Holt. The HI-1587 transceiver features an integrated IP security module necessary to enable the IP. This eliminates the need for a traditional external IP dongle chip, commonly used with other IP solutions. The HI-1587 is also the first MIL-STD-1553 transceiver to have 1.8V, 2.5V and 3.3V compatible digital I/O, making it easier to interface with a broad range of FPGAs.

The Holt IP core product includes the HI-6300 IP Core, a Verilog test bench, and supporting documentation, allowing designers to instantiate the core in a variety of FPGA implementations.

Contact Holt directly for ordering details and information on DO-254 Certification Package supporting Design Assurance Level A.

Software

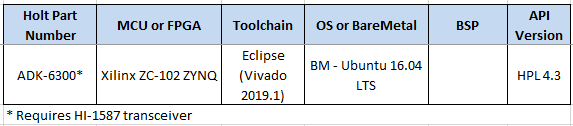

The API Application Development Kit (ADK-6300) includes Holt's MIL-STD-1553 Application Programming Interface (API) library. Details are outlined below.

Features

-

IP is based on fully validated IC solution

-

Concurrent multi-terminal operation

-

High-performance synchronous Host interface

-

HI-1587 transceiver has integrated IP security module

- World’s first MIL-STD-1553 transceiver supporting 1.8V, 2.5V and 3.3V digital I/O

-

50 MHz or 100 MHz input clock

-

8K or 64K words error-correcting code (ECC) RAM with built-in self-test (BIST) feature

-

Fully programmable Bus Controller with 28 op code instruction set

-

Independent time-tag counters for all terminals with 32-bit option for Bus Controller

-

32-deep Interrupt buffer

-

MIL-STD-1760 Boot mode to initialize RT with Busy Bit set without host intervention